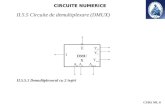

Circuite de Calare a Fazei

Transcript of Circuite de Calare a Fazei

CIRCUITE DE CALARE A FAZEI

147

CAPITOLUL V

CIRCUITE DE CALARE A FAZEI (PLL)

Bucla PLL (Phase-Locked Loop) sau circuitul de calare a fazei reprezintă un sistem cu reacţie,

semnalul de reacţie fiind utilizat pentru a cala, sau sincroniza faza (şi frecvenţa) semnalului de ieşire produs de un oscilator controlat în tensiune (OCT) pe cea a semnalului de intrare. Una din principalele aplicaţii este cea de demodulator MF. În general, demodulatoarele MF clasice conţin bobine sau transformatoare, elemente voluminoase şi costisitoare, care necesită reglaj şi care nu pot fi realizate sub forma unui circuit integrat.

Bucla PLL reprezintă o soluţie economică şi convenabilă din punct de vedere tehnologic a problemei discriminatorului MF, având în plus şi o comportare mai bună decât discriminatoarele MF clasice în condiţiile unui raport S/Z coborât. Odată cu apariţia radiocomunicaţiilor spaţiale, care implică distanţe mari şi puteri limitate de emisie, apare necesitatea realizării recepţiei în condiţii defavorabile (raport S/Z mic) şi se pun probleme de refacere şi condiţionare a semnalului recepţionat, referitoare la eliminarea efectului Doppler şi filtrarea zgomotelor. Bucla PLL răspunde acestor cerinţe, putând realiza urmărirea semnalului (tracking), filtrarea şi demodularea sa precum şi extragerea purtătoarei sau a unei subpurtătoare pentru detecţie, operaţie cunoscută sub numele de sincronizare.

În general, bucla PLL are schema bloc prezentată în figura 5.1, având trei elemente funcţionale: un comparator de fază (CF), un FTJ şi un oscilator controlat în tensiune (OCT).

Comparatorul sau detectorul de fază furnizează un semnal proporţional cu diferenţa de fază a semnalelor aplicate la cele două intrări ale sale (semnalul de intrare luat ca referinţă şi semnalul generat local de OCT). În general vom considera CF de tipul multiplicator, care realizează efectiv produsul celor două semnale aplicate la intrările sale, astfel că dacă la intrare nu se aplică semnal, semnalul de ieşire este zero. În paragraful V.4 sunt prezentate şi alte tipuri de CF.

OCT este comandat cu tensiunea de eroare generată de CF şi filtrată de filtrul buclei, pentru ca acesta să-şi varieze frecvenţa şi faza (integrala frecvenţei) în scopul reducerii la minim a defazajului dintre semnalul de intrare şi cel generat local (de OCT).

Dacă frecvenţa semnalului de intrare variază, cea a OCT-ului urmăreşte în medie aceste variaţii. Fie caracteristica de transfer a OCT-ului cea reprezentată în fig.5.2. Dacă în absenţa tensiunii de control (Uc = 0) OCT-ul oscilează pe

Figura 5.1 Schema buclei PLL

Figura 5.2 Caracteristica OCT

Capitolul V

148

frecvenţa f0 iar la intrare vom aplica un semnal la frecvenţa f1 , pentru ca bucla să se poată cala (OCT să oscileze pe frecvenţa f1) ea va trebui să-şi construiască o componentă de c.c. Uc1. De fapt, tensiunea de control, în situaţia când bucla este calată, va prezenta fluctuaţii în jurul acestei valori, dar valoarea medie a semnalului va fi Uc1. Putem considera acest proces compus din:

Construirea unei componente de c.c. de valoare medie Uc1, necesară pentru a asigura intrarea în calare a buclei, regim tranzitoriu denumit CAPTURĂ sau ACHIZIŢIE, caracterizat deci prin existenţa unei componente de c.c. Uc1, de valoare diferită de zero;

Producerea unei componente de c.a., suprapusă peste Uc1, de valoare medie zero, care asigură menţinerea în sincronism a buclei (de fapt, tensiunea de control este uşor diferită de zero, iar bucla lucrează cu o eroare de fază destul de mică).

Cele expuse sunt evident valabile pentru un semnal de intrare de frecvenţă constantă, orice variaţie a acesteia implicând variaţia componentei de c.c. Uc1 a tensiunii de eroare. Utilizând terminologia specifică amplificatorului diferenţial, putem denumi cele două componente de mod comun şi de mod diferenţial.

Ce se întâmplă în cazul când semnalul de intrare este perturbat de zgomot aditiv? Evident, bucla PLL trebuie să reproducă semnalul original, înlăturând cât mai mult din efectul zgomotului. În acest scop CF compară faza semnalului recepţionat cu cea a semnalului produs de OCT, obţinându-se un semnal de eroare, afectat de zgomot. Zgomotul este un proces aleator, de valoare medie nulă, intervalul de timp pe care se face observaţia trebuie însă să fie destul de mare. Filtrul de după CF, prin acţiunea sa de mediere, micşorează influenţa zgomotului.

Evident, dacă semnalul recepţionat are frecvenţa stabilă, cantitatea de informaţie necesară pentru sincronizare este mică şi se poate folosi un filtru care mediază semnalul pe o durată mare. Dacă semnalul recepţionat este modulat în frecvenţă sau fază, banda este mai largǎ şi evident se va reduce intervalul pe care se face medierea (durata intervalului elementar), iar influenţa zgomotului nu mai este neglijabilă. În general, bucla PLL poate fi considerată un filtru care îmbunătăţeşte calitatea semnalului procesat, micşorând influenţa zgomotului. Parametrii buclei PLL sunt următorii:

1. Frecvenţa liberă de oscilaţie f0 (ω0) (free-running frequency, center frequency) este frecvenţa pe care oscilează OCT (VCO) în absenţa semnalului de intrare (bucla nu este calată).

2. Domeniul de urmărire 2fu (2 ωu) sau menţinere (lock-range, hold-in range - 2fu, tracking range - fu) este definit ca domeniul în care poate varia frecvenţa semnalului de intrare astfel încât bucla să rămână în calare.

3. Domeniul de captură 2fc (2 ωc) sau achiziţie (capture range, lock-in range-fc) este domeniul semnalului de intrare, în jurul frecvenţei f0, în care bucla se poate cala pe semnalul de intrare. Dacă bucla ar fi ideală ar coincide cu cel de urmărire. În general fc < fu, bucla nu mai poate intra în calare la extremităţile domeniului de urmărire (fig.5.3).

4. Câştigul detectorului de fază - kd reprezintă raportul dintre tensiunea la ieşirea CF şi defazajul dintre semnalul de intrare şi cel al OCT. Se măsoară în [V/rad] şi pentru nivele mici ale semnalului de intrare depinde şi de amplitudinea acestuia.

5. Factorul de conversie al OCT - k0, reprezintă raportul dintre frecvenţa OCT şi tensiunea sa de comandă. Se măsoară în [rad/sec/V].

Figura 5.3 Domeniile buclei i PLL

CIRCUITE DE CALARE A FAZEI

149

6. Amplificarea buclei 0 dk k k= ⋅ este produsul tuturor amplificărilor în c.c. ale elementelor

buclei. Se măsoară în [sec-1]. 7. Pragul de sensibilitate sau detecţie – reprezintǎ nivelul minim al semnalului de intrare necesar

menţinerii calării.

V.1 Problema sincronizării Referindu-ne la bucla PLL, să facem o analogie cu sincronizarea a două mişcări de rotaţie

mecanice (doi arbori, două roţi, etc.) prima fiind mişcarea de referinţă (semnal de intrare), iar pe cea de-a doua dorind s-o aducem în sincronizare cu prima (fig.5.4).

În acest scop trebuie să dispunem de informaţia care să ne arate în ce sens trebuie să acţionăm asupra celei de-a doua mişcări (accelerare sau frânare), şi în ce moment a obţinut sincronizarea. Evident, prin proiecţia fazorului asociat mişcării de rotaţie pe cele două axe de coordonate x şi y, obţinem două oscilaţii sinusoidale defazate în cuadratură.

Faza oscilaţiilor sinusoidale este o mărime relativă ce poate fi măsurată numai în raport cu o referinţă. Prin proiecţia celor doi fazori pe axa x obţinem:

]cos[)(cos ii tt θωθ += (5.1)

]cos[)(cos 00' θωθ += tt (5.2)

unde ωi, ω0 - pulsaţiile (viteze de rotaţie unghiulară) ale celor două mişcări: θi, θ0 - fazele iniţiale ale semnalelor.

Să presupunem că putem măsura diferenţa de fază exprimată prin: ])cos[()]()(cos[ 00

' θθωωθθ −+−=− ii ttt (5.3)

folosind configuraţia din figura 5.5, bazată pe formula trigonometrică

)cos(21)cos(

21coscos βαβαβα ++−=⋅ (5.4)

Se observă că întrucât funcţia cosinus este pară (fig.5.5), cosφ = cos(-φ), ea nu poate specifica semnul defazajului, avans sau întârziere, deci nu ştim cum trebuie acţionat pentru a sincroniza cele două mişcări.

O informaţie utilă pentru sincronizare s-ar putea căpăta măsurând cosinusul diferenţei de fază la două momente de timp diferite t şi t0, şi observând cum a evoluat (creştere sau scădere).

Figura 5.4 Sincronizarea a două mişcări de rotaţie

Figura 5.5 Ilustrarea detecţiei de fază cu defazaj zero

Capitolul V

150

Dar )/()]()([ 00 tttftf −− la limită când t → t0, este derivata funcţiei f(t), şi se observă că,

pentru sincronizare ar trebui să obţinem ( ) φφ sincos ' −= , adică o funcţie cu simetrie impară, de

tipul )]sin([sin φφ −−= (figura 5.6).

Aceasta se realizează prin decalarea în avans a referinţei de timp cu Δt, ţinând cont şi de întârzierea introdusă de filtru.

Dacă 2

cos π=Δt , obţinem

)(sin2

)(cos '' tt θπθ =⎥⎦⎤

⎢⎣⎡ − (5.5)

iar produsul celor două semnale va fi de forma:

]sin[21]sin[

21cossin θ(t)(t)θθ(t)(t)θθ(t)(t)θ ''' ++−= (5.6)

EXEMPLUL V.1 Să demonstrăm pentru bucla PLL cu CF de tip multiplicator, bazându-ne pe condiţia ca bucla calată să aibă componenta de c.c. de mod diferenţial nulă, că defazajul dintre semnalul de intrare şi cel de la ieşirea OCT este π/2.

Am văzut că semnalul de eroare obţinut la ieşirea FTJ de după CF tip multiplicator este de forma:

[ ] φθθ cos21)()(cos

21 ' =− tt

În situaţia în care bucla este calată, componenta de mod diferenţial trebuie să fie nulă, aceasta va conduce la

condiţia 2

0cos21 πφφ =→= , adică o defazare în

cuadratură a semnalului de la ieşirea OCT faţă de cel de la intrare.

Dacă la ieşirea FTJ se obţine valoarea zero, cele două

semnale sunt sincronizate exact în frecvenţă, iar defazajul dintre ele este π/2.

Spunem că cele două semnale sunt în coerenţă de fază, sau OCT este calat pe semnalul de intrare, situaţie în care semnalul de eroare are o valoare medie nulă (fig.5.7).

S-a presupus semnalul de intrare de frecvenţă constantă.

Figura 5.7 Valoare medie nulă

Figura 5.6 Ilustrarea detecţiei de fază cu referinţa decalată în cuadratură

CIRCUITE DE CALARE A FAZEI

151

Defazajul de π/2 în situaţia de calare, între semnalul de intrare în buclă şi cel de la ieşirea OCT, este valabil doar pentru semnal de intrare pur sinusoidal sau undă rectangulară cu coeficient de umplere 0,5 şi CF de tip multiplicator. Alte tipuri de CF conduc la defazaje în situaţia de calare cu alte valori (de exemplu 0o, 180o, etc.).

În cazul în care semnalul de intrare este rectangular, dar cu un coeficient de umplere diferit de 1/2, apare situaţia descrisă în figura 5.8. În această situaţie defazajul are o valoare care să determine o componentă dinamică nulă când bucla este calată.

EXEMPLUL V.2 Să calculăm valoarea defazajului când bucla este calată, pentru semnal de intrare de tip undă rectangulară cu coeficient de umplere r, situaţie descrisă în figura 5.8. Evident,

π→φ→

→φ→

π=π=π⋅=φ

1r00r

rTT

2T

2/T 11

Se observă că o mică variaţie a defazajului semnalului 2 faţă de 1, în jurul situaţiei descrise, conduce la apariţia unei componente de c.c. care poate provoca ieşirea din calare a buclei, deoarece regiunile I şi II nu se mai compensează. În această situaţie trebuie evitată folosirea CF de tip multiplicator, preferându-se un CF realizat cu bistabile. Se observă de aici că funcţionarea buclei depinde şi de tipul comparatorului de fază folosit. În general există mai multe tipuri de CF, fiecare prezentând anumite proprietăţi. Principalele tipuri de CF sunt trecute în revistă în paragraful V.4.

Să arătăm că bucla PLL cu CF de tip multiplicator poate asigura calarea şi pe o armonică impară de ordin n a semnalului de intrare (n = 3, 5, 7, …).

Fie situaţia reprezentată în figura 5.9 pentru n = 3. Se observă că semnalul 2 de la ieşirea OCT este defazat cu π/2 faţă de cel de la intrare (un sfert de perioadă), ceea ce conduce la componenta de c.c. de mod diferenţial nulă.

Din cele 3 perioade ale semnalului dat de OCT, pe durata T a semnalului de intrare, două se compensează, dând componenta de c.c. nulă, iar una asigură semnalul necesar sincronizării. Se observă deci că amplitudinea acestuia este 1/3 faţă de cazul în care n = 1, şi în general 1/n pentru n oarecare impar.

Figura 5.8 Coeficient de umplere defavorabil

Figura 5.9 Calarea pe armonica a 3-a a semnalului

Capitolul V

152

Variaţia coeficientului de umplere r al semnalului de intrare, în jurul valorii de 50 %, în limite mici, nu afectează prea mult procesul de calare, defazajul între semnalele 1 şi 2 devenind rπ.

EXEMPLUL V.3 Să calculăm valoarea minimă a coeficientului de umplere al semnalului de tip undă rectangulară aplicat la intrare, pentru care bucla PLL cu CF de tip multiplicator nu mai poate asigura calarea. Evident, lăţimea lobului mic al semnalului de intrare nu poate să scadă sub o perioadă a semnalului dat de OCT, întrucât nu s-ar mai putea face compensarea indicată. Deci,

T = rT > T/3 → r > 1/3

sau în cazul general: r > 1/n. Defazajul φ = rπ trebuie să satisfacă condiţia φ > π/n.

Să arătăm acum că bucla PLL cu CF de tip

multiplicator nu poate asigura calarea pe armonici pare ale semnalului de intrare (n = 2, 4, …). Fie situaţia reprezentată în figura 5.10, pentru n = 2.

Se observă că de această dată compensarea ar trebui făcută pe semiperioadă, componenta de c.c. de mod diferenţial rezultând nulă din contribuţia ambelor semiperioade Aceasta ar implica un coeficient de umplere r de 50% pentru ambele semnale. Orice abatere a coeficientului de umplere r al semnalului 1 sau 2 în jurul acestei valori va conduce la o componentă de c.c. de mod diferenţial nenulă şi deci bucla nu se va mai putea cala. Pe de altă parte, semnalele de eroare nu mai au polarităţi alternante ( −+−+ ) în jurul flancurilor semnalului ci apar ca −−++ .

Orice eroare de fază (deplasare la dreapta sau la stânga faţă de poziţia de echilibru) implică creşterea lobilor pozitivi în dauna celor negativi sau invers. Funcţionarea buclei este nesigură şi nu se poate face multiplicare de frecvenţă pe armonicile pare (prin această metodă).

Am văzut că bucla PLL are configuraţia din figura 5.11. Circuitul încadrat cu linie punctată este similar cu un detector sincron. Defazajul de π/2 este specific doar buclei PLL cu detector de fază de tip multiplicator. În lipsa semnalului de intrare tensiunea de control UC a OCT este nulă, acesta lucrând pe frecvenţa liberă de oscilaţie, pentru OCT putându-se scrie relaţia:

CUKdt

td0

' )(=

θ (5.7)

sau aplicând transformata Laplace: )()( 0

' sUKss C=θ (5.8)

de unde:

s

sUKs C )(

)( 0' =θ (5.9)

Relaţia 5.8 ne arată că faza OCT este proporţională cu integrala tensiunii de control UC. Bucla fiind comandată în fază, tensiunea de control este proporţională cu diferenţa de fază, iar OCT se va comporta ca un integrator.

Figura 5.11 Configuraţia buclei PLL

Figura 5.12 Modelul neliniar al buclei PLL

Figura 5.10 Calarea pe armonici pare

CIRCUITE DE CALARE A FAZEI

153

Vom demonstra acum că semnalul de eroare obţinut la ieşirea CF determină menţinerea calării buclei; în acest scop vom presupune o buclă PLL cu CF de tip multiplicator urmat de un FTJ care să dea la ieşire sinusul diferenţei de fază a semnalelor de intrare (figura 5.11).

Atunci bucla poate fi modelată de circuitul din figura 5.12, denumit model neliniar (blocul care determină funcţia sinus fiind în mod evident neliniar). Fie semnalul de intrare:

)](cos[)( ttAtxi θω += (5.10)

iar ieşirea OCT:

)]t(tsin[A)t(e '00 θ+ω= (5.11)

În condiţiile precizate, semnalul de la ieşirea CF este:

[ ])t()t(sinKAA21)t(U '

d0d θ−θ= (5.12)

unde Kd este câştigul detectorului de fază. Conform relaţiei (5.9) avem:

)t(UKdt

)t(dC0

'=

θ (5.13)

sau

ττθ dUKt Ct )()( 0

' ∫= (5.14)

Presupunând bucla calată, eroarea de fază θ(t) - θ'(t) este mică şi putem aproxima:

)t()t()]t()t(sin[ '' θ−θ=θ−θ (5.15) ceea ce permite să neglijăm neliniaritatea sistemului, bucla PLL fiind în acest caz un sistem automat cu reacţie, de tip liniar, uşor de analizat.

Presupunând o buclă PLL neliniară de ordinul I fără filtru, putem scrie:

)]t()t(sin[KAA21)t(U '

d0C θ−θμ= (5.16)

atunci amplificarea totală de c.c. a buclei va fi:

0d0 KKAA21K μ= (5.17)

iar relaţia (5.14) devine:

ττθτθθ dKt t )]()(sin[)( '' −= ∫ (5.18)

Prin diferenţiere se obţine:

)]t()t(sin[kdt

)t(d ''

θ−θ=θ

(5.19)

Vom presupune că semnalul de intrare în buclă este un semnal ce prezintă un salt de frecvenţă Δω = dθ/dt, şi notăm eroarea de fază:

)t()t()t( ' φ=θ−θ (5.20) Atunci,

)0()(sin'

≥=−Δ=−= ttkdtd

dtd

dtd

dtd φ

φω

φθθ (5.21)

sau

Figura 5.13 Traiectorie în planul fazelor

Capitolul V

154

ωΔ=φ+φ )t(sink

dtd

(5.22)

Ea este ecuaţia diferenţială neliniară a buclei PLL de ordinul I reprezentată în figura 5.13. Reprezentarea dφ/dt în funcţie de φ este cunoscută sub denumirea de traiectoria în planul fazelor.

Dacă bucla PLL a lucrat cu eroare de fază şi frecvenţă zero, înainte de aplicarea saltului de frecvenţă Δω, eroarea de frecvenţă devine Δω şi punctul iniţial de funcţionare este B (vezi figura 5.13); s-a presupus Δω > 0. Pentru a stabili sensul de mişcare pe traiectorie observăm că, deoarece Δt > 0, pentru ca dφ/dt > 0 este necesar ca dφ > 0, adică în semiplanul superior φ creşte, iar punctul de funcţionare se mişcă pe traiectorie de la stânga la drepta, în timp ce în semiplanul inferior dφ/dt < 0, φ scade şi punctul se mişcă de la dreapta la stânga.

Punctul A este un punct stabil de funcţionare, o abatere în jurul lui conducând la întoarcerea în punctul A şi este cunoscut ca punct de funcţionare în regim permanent. El este caracterizat de eroarea de fază de regim permanent φp, (φp ≠ 0) şi de eroarea de frecvenţă de regim permanent care este egală cu zero. În schimb, din aceleaşi motive, punctul C este un punct instabil de funcţionare.

În situaţia de calare, conform celor discutate, eroarea de frecvenţă de regim permanent este zero,

0=dtdφ (5.23)

iar ecuaţia (5.22) devine:

k

)t(sin ωΔ=φ (5.24)

Evident, bucla poate cala doar dacă:

1k

<ωΔ (5.25)

Rescriind ecuaţia (5.22) sub forma:

)t(sinkk

dtd

φ−ωΔ

=

φ

(5.26)

se obţine reprezentarea din figura 5.14. Dacă,

1k

<ωΔ (5.27)

în fiecare interval de variaţie a lui φ de lăţime 2π (faza se reduce modulo – 2π) există două puncte de trecere prin zero a lui dφ/dt, când frecvenţa semnalului de intrare coincide cu cea a OCT.

Înainte de calare dφ/dt = 0, iar φ trebuie să varieze monoton crescător sau descrescător şi va lua o valoare corespunzătoare unui punct stabil de funcţionare dacă Δω < k, bucla se calează iar eroarea de fază φ devine egală cu cea de regim permanent.

Având în vedere că în fiecare perioadă există un singur punct de funcţionare stabil, φ nu poate varia cu mai mult de o perioadă până la intrarea în calare, iar bucla PLL de ordinul I achiziţionează rapid, timpul de achiziţie, în general fiind:

k3tacq = (5.28)

şi depinde de valorile iniţiale ale defazajului φ şi frecvenţei.

Figura 5.14 Altă reprezentare în planul fazelor

Figura 5.15 Semnal de eroare

CIRCUITE DE CALARE A FAZEI

155

V.2 Procesul de captură

Fie bucla PLL din figura 5.1, având un OCT cu caracteristica de transfer prezentată în figura 5.2. Aşa cum s-a arătat mai sus, pentru ca bucla să se poată cala, este necesar să-şi construiască o componentă de c.c. UC, pozitivă sau negativă, după cum f1 este mai mare, respectiv mai mică decât f0.

Procesul tranzitoriu asociat capturii este foarte complex şi ar putea fi descris calitativ în modul următor. Considerăm semnalul de intrare sinusoidal de forma Acos(2π fi t+θi ) de frecvenţă constantă şi bucla întreruptă, astfel ca OCT să oscileze pe frecvenţa liberă de oscilaţie f0, furnizând semnalul cos(2π f0 t+θ0 ), iar la ieşirea CF obţinem:

[ ] [ ]0000

00

)(2cos2

)(2cos2

)2cos()2cos(

θθπθθπ

θπθπ

++++−+−

=++

iiii

ii

tffAtffAtftfA

(5.29)

Dacă 0ff i ≅ atunci 00 ≅− ff i , iar

00 ffff ii +<<− (5.30)

ceea ce face ca la ieşirea FTJ să avem practic doar prima componentă:

[ ]00 )(2cos2

)( θθπ −+−= ii tffAtx (5.31)

Fie: dtdf φ

π21

=Δ (5.32)

unde Δf este abaterea instantanee între frecvenţa semnalului de intrare fi şi cea a OCT fov, ultima fiind variabilă, iar φ este valoarea instantanee a defazajului dintre semnalul de intrare şi cel de la ieşirea OCT.

Dacă vom închide bucla, OCT va produce un semnal modulat în frecvenţă de semnalul x(t), mărimea Δf devenind o funcţie de timp.

Dacă închiderea buclei are loc în alternanţa pozitivă a lui x(t) – regiunea I din figura 5.15, fov se apropie de fi. Conform figurii 5.13 (UC pozitivă), Δf scade, iar dφ/dt descreşte şi ieşirea CF devine o funcţie de timp lent variabilă. În timpul alternanţei negative a lui x(t), fov se îndepărtează de fi, Δf creşte, dφ/dt creşte, iar ieşirea CF devine o funcţie de timp rapid variabilă.

În figura 5.16 este reprezentată caracteristica atenuare-frecvenţă a FTJ şi cele 2 regiuni I şi II corespunzătoare situaţiei descrise anterior.

Corespunzător defazajului iniţial, procesul de achiziţie (captură), poate fi mai scurt (intrare în regiunea I), sau mai lung (intrare în regiunea II).

Datorită diferenţei între atenuările introduse de FTJ în regiunile I şi II, în semnalul de eroare se introduce o componentă de c.c. Fără pretenţii de exactitate, acest proces este ilustrat în figura 5.17.

Componenta de c.c. introdusă astfel, într-o perioadă a semnalului x(t) determină apropierea frecvenţei OCT fov de frecvenţa semnalului de intrare fi, scăderea valorii semnalului de eroare x(t) proporţională cu diferenţa fvo – fi, şi apropierea frecvenţei OCT de cea a semnalului de intrare (fi). Procesul este convergent, în final OCT oscilând pe frecvenţa fi, Δf este zero iar sistemul a achiziţionat (calare de fază). În figura 5.18 este ilustrată această situaţie, aşa cum poate fi observată pe osciloscop.

Figura 5.16 Caracteristica FTJ

Capitolul V

156

De remarcat că pe măsură ce frecvenţa OCT fvo se apropie de fi, Δf scade, iar la ieşirea x(t) a FTJ se obţine un semnal cu o atenuare tot mai mică, ceea ce explică creşterea amplitudinii oscilaţiei.

Putem remarca, pe baza figurii 5.18, formele de undă 2 şi 3, că procesul de captură se întinde pe un număr n de perioade ale semnalului de intrare; n este cu atât mai mic cu cât filtrul buclei este de bandă mai largă şi mai puţin selectv.

Un filtru foarte selectiv, cu o caracteristică atenuare – frecvenţă foarte abruptă, face imposibilă achiziţia, având în vedere faptul că nu se poate construi componenta de c.c. din procesul de MF şi asimetria caracteristicii FTJ. Un filtru cu constantă mare de timp (bandă îngustă) ar face ca numărul n de perioade în care se construieşte componenta de c.c. şi respectiv timpul de achiziţie să fie foarte mare. În ambele cazuri, achiziţia poate fi uşurată intervenind din exterior.

V.3 Tehnici de achiziţie rapidă

Pentru ca bucla să se poată cala, ea trebuie să-şi construiască o componentă de c.c. care să forţeze OCT să oscileze pe frecvenţa semnalului de intrare. Acest proces de generare a componentei de c.c. implică un timp destul de mare, adică folosirea unui FTJ cu o caracteristică lent căzătoare.

Dacă bucla este folosită ca circuit de sincronizare, evident FTJ va trebui să fie selectiv şi de bandă îngustă, ceea ce face imposibilă sincronizarea fără ajutor din exterior. În celelalte cazuri, timpul mare de intrare în achiziţie poate constitui un dezavantaj. De aceea s-au dezvoltat tehnicile de achiziţie rapidă, ce determină reducerea timpului de achiziţie şi asigurarea sincronizării în cazul când achiziţia ar fi imposibilă. Principalele tehnici de achiziţie rapidă sunt:

A. Cu discriminator MF montat în paralel cu CF.

B. Transformarea buclei PLL în bucla de ordinul I.

C. Cu rampă de tensiune aplicată la intrarea OCT.

D. Mărirea amplificării de c.c. a buclei.

Figura 5.18 Ilustrarea procesului de achiziţie al buclei PLL

Figura 5. 17 Diferenţe de atenuare între lobi

CIRCUITE DE CALARE A FAZEI

157

V.3.1 Discriminator MF în paralel cu comparatorul de fază

Această metodă este una din cele mai răspândite, fiind uşor de implementat, însă implică o anumită calitate a semnalului de intrare (raport semnal/zgomot), deoarece discriminatorul MF este un circuit necoerent. Ca o regulă empirică, raportul S/Z trebuie să fie peste 6 dB şi să se renunţe la această tehnică dacă S/Z este sub 0 dB. Metoda este ilustrată în figura 5.19.

Pentru a achiziţiona, OCT trebuie să-şi varieze frecvenţa de la valoarea f0 la fi, caracteristica sa fiind ilustrată în fig.5.2, bucla construind componenta de c.c. de valoare Ui.

Discriminatorul MF, acordat pe frecvenţa f0, atacat de un semnal cu frecvenţa fi, furnizează la ieşire o componentă de c.c. de valoare Ui’ foarte apropiată de Ui, care determină OCT să oscileze pe frecvenţa fi’ foarte apropiată de fi, deci bucla poate achiziţiona.

Discriminatorul MF în acest caz trebuie să dea doar o componentă de c.c. proporţională cu diferenţa fi - f0. În acest scop se poate folosi schema din figura 5.20, denumită cuadricorelator.

Semnalul de ieşire conţine o componentă de c.c. proporţională cu diferenţa fi - f0. Altă implementare a acestei tehnici ar fi folosirea CF tip detector fază-frecvenţă (vezi par. V.3.3).

V.3.2 Transformarea buclei PLL în buclă de ordinul I

Bucla PLL de ordinul I (fără filtru) asigură, aşa cum s-a arătat, o achziţie rapidă a frecvenţei (într-o perioadă a semnalului de intrare), dar introduce o eroare de fază (de urmărire).

Figura 5.21 Bucla PLL de ordin 1 şi 2

Figura 5.19 Tehnica de achiziţie rapidă utilizând un discriminator MF

Figura 5. 20 Schema unui circuit cuadricorelator

Capitolul V

158

În principiu, această metodă de achiziţie rapidă ar putea fi implementată cu ajutorul schemei din figura 5.21. Dacă bucla nu este calată, la ieşirea CF se vor obţine bătăi pe frecvenţa fi - f0. Diodele D1 şi D2, acţionează ca nişte întrerupătoare aproape ideale (sunt montate în buclă), intrând în conducţie datorită componentei alternative ce apare în situaţia în care bucla nu este calată şi determină scurt-circuitarea rezistenţei Ri.

Bucla devine fără filtru (de ordinul I) şi achiziţionează rapid, componenta de c.a. dispare şi diodele se blochează.

V.3.3 Cu rampă de tensiune aplicată la intrarea OCT

În această variantă de achiziţie rapidă se variază frecvenţa OCT, baleind domeniul de frecvenţă în care se poate afla semnalul de intrare. În momentul în care f0 concordă cu fi, bucla se va cala. Metoda este reprezentată în figura 5.22. În general, viteza de baleiaj b trebuie să satisfacă condiţia:

2nfb <

unde fn – frecvenţa naturală a buclei. Baleiajul se poate face cu bucla deschisă, închiderea ei făcându-se în momentul sesizării apropierii

frecvenţei OCT de fi sau cu bucla închisă, variantă ce este preferată. Varianta optimă de realizare a baleiajului de frecvenţă este aceea a utilizării unui generator de

curent constant care să atace integratorul buclei, ca în figura 5.23. Semnalul de ieşire din integrator este o rampă de tensiune, cu panta determinată de constanta de

timp a integratorului şi intensitatea curentului constantă.

Se preferă această variantă de atac în reacţie la joncţiunea lui R2 cu C, deoarece atacul la intrarea

AO ar conduce la apariţia la ieşire a unui semnal treaptă asociat pornirii şi opririi generatorului de curent constant, ceea ce ar putea provoca ieşirea din calare a buclei.

În situaţia în care bucla este calată, efectul curentului injectat este compensat prin crearea unei componente de c.c. la ieşirea CF, astfel că nu este necesară deconectarea generatorului.

Figure 5.22 Achiziţie rapidă cu rampă de tensiune

Figura 5.23 Implementarea metodei cu rampă de tensiune

CIRCUITE DE CALARE A FAZEI

159

V.3.4 Mărirea amplificării de c.c. a buclei Fie caracteristica FTJ al buclei, reprezentată în figura 5.24. Dacă diferenţa fi - f0 este mare (situaţia

I), semnalul de la ieşirea CF este puternic atenuat, bucla în acest caz nu-şi mai poate construi componenta de c.c. care să-i asigure calarea.

În situaţia II acest lucru este posibil. Diferenţa de nivel între semnalele I şi II poate fi compensată cu un amplificator de c.c., care însă va afecta domeniul de urmărire, micşorându-l. Această tehnică de achiziţie rapidă poate fi implementată cu ajutorul schemei din figura 5.25.

Amplificatorul de c.c. îşi poate varia amplificarea de la o valoare minimă (C = 0) specifică unei

funcţionări normale, la o valoare mare (C = 1) în timpul achiziţiei. Când bucla a achiziţionat, amplificarea trebuie să revină la o valoare mică, pentru a nu afecta domeniul de urmărire.

Acelaşi efect ar putea fi obţinut prin creşterea benzii filtrului în perioada de achiziţie, urmată de revenire la normal.

Un circuit de sesizare a calării (indicator de calare) este prezentat în figura 5.26. Când bucla este calată, semnalul de la ieşirea OCT este în fază cu cel de intrare, iar la ieşirea detectorului sincron exterior buclei vom obţine o componentă de c.c., care este sesizată cu ajutorul comparatorului.

Componenta de c.c. nu poate apare decât în situaţia când bucla este calată şi rezultă datorită faptului că:

21cossin 22 == xx

filtrul trece jos (FTJ) de la ieşirea multiplicatorului din afara buclei având rolul de circuit de mediere.

Figura 5.26 Un indicator de calare

Figura 5.24 Caracteristica FTJ Figura 5.25 Variaţia amplificării de c.c.