t6

-

Upload

dragos-drg -

Category

Documents

-

view

2 -

download

1

description

Transcript of t6

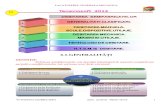

TEMĂ PROIECT Nr.6

Fie funcţiile booleene f1 şi f2 date prin tabelul de adevăr de mai jos.Se cere:

a) Să se exprime funcţiile date prin FCD (forma canonică disjunctivă), FCC (forma canonică conjunctivă) şi diagrame Karnaugh.

b) Să se obţină ambele forme minime (disjunctivă şi conjunctivă) ale funcţiilor, utilizându-se metoda diagramelor Karnaugh, respectiv metoda Quine-McCluskey.

c) Să se obţină formele minime disjunctive ale celor două funcţii logice, folosindu-se metoda minimizării ansamblului.

d) Să se implementeze funcţiile logice, independent, numai cu porţi logice ŞI-NU (porţile logice sunt realizate în tehnologia TTL).

e) Să se implementeze funcţiile logice, independent, numai cu porţi logice SAU-NU (porţile logice sunt realizate în tehnologia CMOS).

f) Să se implementeze ansamblul funcţiilor logice numai cu porţi logice ŞI-NU (porţile logice sunt realizate în tehnologia TTL).

g) Să se implementeze ansamblul funcţiilor logice cu MUX-uri de 8 respectiv 16 căi (circuitele sunt realizate în tehnologia .........).

h) Să se implementeze ansamblul funcţiilor logice cu DMUX-uri de 8 respectiv 16 căi şi porţi logice ŞI-NU în prima variantă, respectiv ŞI în a doua variantă (toate circuitele sunt realizate în tehnologia .........).

i) Să se calculeze timpii de propagare „intrare-ieşire”, pentru toate schemele logice obţinute.

j) Să se calculeze puterile disipate pentru toate schemele logice obţinute.k) Să se compare soluţiile de implementare obţinute.l) Se va face analiza, prin simulare, a tuturor schemelor logice obţinute utilizându-se

pachetul de programe OrCAD.Pe schemele logice obţinute se vor specifica tipul şi gradul de utilizare al fiecărui circuit integrat.

x1 x2 x3 x4 f1 f2

0 123456789

101112131415

0 0 0 00 0 0 10 0 1 00 0 1 10 1 0 00 1 0 10 1 1 00 1 1 11 0 0 01 0 0 11 0 1 01 0 1 11 1 0 01 1 0 11 1 1 01 1 1 1

*1*0111111100001

**100*0*11100110

![O mare de lacrimi - Ruta Sepetys - Libris.ro mare de lacrimi - Ruta Sepet… · IWIUf,V'I:IC EUVW O.l?rnglnt [qIzI^ 15 rfr.rpu qq3o nr pur-npultrrd'pdec leerpu z-t6 plaiaryB ']u gaJlul](https://static.fdocumente.com/doc/165x107/5f97d328be3fa70aaa026463/o-mare-de-lacrimi-ruta-sepetys-mare-de-lacrimi-ruta-sepet-iwiufviic-euvw.jpg)