Aemc Proiect Alin

-

Upload

christian-dee -

Category

Documents

-

view

218 -

download

0

Transcript of Aemc Proiect Alin

-

8/15/2019 Aemc Proiect Alin

1/8

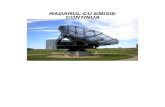

Universitatea Tehnica

“Gh. Asachi” Iasi

Facultatea de Electronica,

Telecomunicatii si Tehnologia

Informatiei

Indrumator: Student:

Conf. Dr. Ing. Adumitroaei Alin-IonutVornicu Liliana Grupa 5305

-

8/15/2019 Aemc Proiect Alin

2/8

Date de proiectare:

• valoarea maxima a raportului de transmisie !"#

• numarul de $ecimale cu care se face afisarea %#

• afisare de tip &argraph din ! in !.

Prezentare generala

Aparatul este destinat masurarii raportului de transmisie la cutii de vite$e, atat pentruca$ul valorilor fixe 'cu trepte( cat si pentru valori varia&ile 'in ca$ul sistemelor variatoare(.

)chema &loc a aparatului se pre$inta in figura urmatoare

In acest ca$ este o schema de frecventmetru digital ce determina numarul de impulsuri

de pe canalul A care trec spre numarator in timpul de poarta, o&tinut prin divi$area perioadei

semnalului de pe canalul * cu !"+, fiind ales in functie de numarul de $ecimale cu care se

face afisarea. -umarul afisat - re$ulta din relatia

-

8/15/2019 Aemc Proiect Alin

3/8

- 'T*/!"(0TA 'nA0n*(/!"

unde

TA 1 perioada semnalului de pe canalul AT* 1 perioada semnalului de pe canalul *

1 numarul de $ecimale

nA 1 turatia ar&orelui de pe canalul A

n* 1 turatia ar&orelui de pe canalul *

2u aceste relatii vom calcula parametrii aparatului, conform datelor de proiectare impuse

Error 3eference source not found - 'T*/!"

(0TA 'nA0n*(/!" !"/!"% !"4

Blocuri functionale. Schema de lucru si principii de functionare

Blocul formator :

*locul formator este format dintr5un Trigger )chmitt cu porti neinversoare. 2ircuitul

folosit este MMC4050

*locul formator are rolul de a adapta semnalul provenit de la traductor cu un semnal

compati&il cu circuitele numerice si de a reface fronturile a&rupte ale impulsurilor. El se

-

8/15/2019 Aemc Proiect Alin

4/8

conectea$a la iesirea traductorului de impulsuri, iar impulsurile 6formate” sunt aplicate portii

7AD8.

Circuitul poarta:

2ircuitul poarta este alcatuit de o poarta 9AD8 cu doua intrari. :e prima intrare sunt

aplicate impulsurile provenite de la formatorul A, pe a doua intrare sunt aplicate impulsurile

provenite de la divi$orul de frecventa, inversate de o poarta 9!"8. Impulsurile provenite de

la formator sunt validate sa treaca spre &locul numarator numai atunci cand semnalul inversat

provenit de la divi$orul de frecventa se afla in 9!8 logic.

Di#izorul de frec#enta:

;ivi$orul de frecventa este compus din doua circuite de divi$are

-

8/15/2019 Aemc Proiect Alin

5/8

de la formatorul A, dupa care va divi$a aceasta frecventa prin '4. 2and va a>unge la valoarea

&inara corespun$atoare valorii de '4, adica 6$0000”, va produce un impuls de reset pentru

divi$orsi un impuls de cloc= pentru al doilea circuit de divi$are. Al doilea circuit de divi$are,

cu a>utorul portilor 7AD8 cu ? intrari, la aparitia la iesire a codului &inar 6$00$$$000$”,

corespun$ator valorii de 54 'depasire divi$or( va trimite un impuls care va produce resetul

circuitului si impulsul de validare pentru poarta.

umaratorul:

-umaratorul este format din sase numaratoare *2; sincrone reversi&ile, preseta&ile,

de tipul 40$)'. Aceste numaratoare au setate intrarile de Preset *na+le si C, Do-n la 7$8

logic, pentru a nu se incarca paralel, respectiv pentru a numara inainte. 2and numaratorul a

atins numarul maxim numara&il in modul inainte 'respectiv @ pentru $ecimal(, dupa >umatate

din perioada semnalului de tact 'respectiv dupa ce C, P trece in 708( 7C/8 trece la nivel 708

si va da un impuls de cloc= pentru numaratorul urmator aflat conectat in cascada. Astfel,

numaratorul ce primeste un impuls de cloc= de la poarta 7AD8 va numara $ecimile de

miimi, al doilea conectat in cascada cu acesta va numara miimile, al treilea va numara

sutimile, al patrulea va numara $ecimile, al cincilea unitatile, iar ultimul $ecile. Iesirile de

date din numaratoare sunt aplicate circuitelor de decodare si apoi afisate. )chema

numaratorului este pre$entata in continuare

Blocul de decodare si afisare:

4 0 1 9 2

J

1

J

2

J

3

J

4

!

C

"

C

#

R

S

T

Q

1

Q

2

Q

3

Q

4

$

%

C

&

4 0 1 9 2

J

1

J

2

J

3

J

4

!

C

"

C

#

R

S

T

Q

1

Q

2

Q

3

Q

4

$

%

C

&

0 1 9 2

J

1

J

2

J

3

J

4

!

C

"

C

#

R

S

T

Q

1

Q

2

Q

3

Q

4

$

%

C

&

4 0 1 9 2

J

1

J

2

J

3

J

4

!

C

"

C

#

R

S

T

Q

1

Q

2

Q

3

Q

4

$

%

C

&

4 04 0 1 9 2

J

1

J

2

J

3

J

4

!

C

"

C

#

R

S

T

Q

1

Q

2

Q

3

Q

4

$

%

C

&

-

8/15/2019 Aemc Proiect Alin

6/8

Acest &loc este alcatuit din % decodoare de tip 45$$ ce contin driver pentru comanda

celulelor de afisare cu segmente. Ba intrarile 7A B C D8 sunt aplicate semnalele de la iesirile

numaratoarelor, dupa care aceste semnale sunt decodate si afisate pe celulele de afisare.

Aceste decodoare contin intrari de testare afisa> 7"8, stergere a datelor de pe afisa> 7B8,

precum si intrari pentru validare latch7 *1S"2!B*8. )chema &locului de afisare este

urmCtoarea

4 5 1 1

& $ C #

L

T $

I

L

!

a ' ( d e ) *

V

#

#

A B D C E F G

1

& $ C #

L

T $

I

L

!

a ' ( d e ) *

A B D C E F G

4 5 1 1

& $ C #

L

T $

I

L

!

a ' ( d e ) *

V

#

#

A B D C E F G

4 5 1 1

& $ C #

L

T $

I

L

!

a ' ( d e ) *

V

#

#

4 5 1 1

L

T $

I

L

!

e ) *

V

#

#

4 5 1 1

& $ C #

L

T $

I

L

!

a ' ( d e ) *

V

#

#

A B D C E F G E F G A B D C E F G

-

8/15/2019 Aemc Proiect Alin

7/8

-

8/15/2019 Aemc Proiect Alin

8/8

1 0 1 0 6

A

B

D

C

E

F

G

A

B

D

C

E

F

G

4 5 1 1

&$C#

L T

$ IL !

a'(de) *

V # #

7 4 1 1

4 0 1 9 2

J

1

J

2

J

3

J

4

!

C

"

C

#

R

S

T

Q

1

Q

2

Q

3

Q

4

$

%

C

&

1 4 0 2 7

J

C L K

K

Q

Q

S

R

2 2 1 1

I , % " T

2 2 1 1

I , % " T

4 0 1 9 2

J

1

J

2

J

3

J

4

!

C

"

C

#

R

S

T

Q

1

Q

2

Q

3

Q

4

$

%

C

&

4 5 1 1

&$C#

L T

$ IL !

a'(de) *

V # #

1 0 1 0 6

4 5 1 1

&$C#

L T

$ IL !

a'(de) *

V # #

A

B

D

C

E

F

G

1 0 1 0 6

4 0 1 9 2

J

1

J

2

J

3

J

4

!

C

"

C

#

R

S

T

Q

1

Q

2

Q

3

Q

4

$

%

C

&

4 0 5 0

4 5 1 1

&$C#

L T

$ IL !

a'(de) *

V # #

1 0 1 0 6

4 0 1 9 2

J

1

J

2

J

3

J

4

!

C

"

C

#

R

S

T

Q

1

Q

2

Q

3

Q

4

$

%

C

&

7 4 1 1

4 0 4 0

C

L

K

R

S

T

Q

1

Q

2

Q

3

Q

4

Q

5

Q

6

Q

7

Q

8

Q

9

Q

1

0

Q

1

1

Q

1

2

V

C

C

4 0 4 0

C

L

K

R

S

T

Q

1

Q

2

Q

3

Q

4

Q

5

Q

6

Q

7

Q

8

Q

9

Q

1

0

Q

1

1

Q

1

2

V

C

C

A

B

D

C

E

F

G

A

B

D

C

E

F

G

4 0 5 0

4 5 1 1

&

$C#

L T

$ IL !

a

'(de) *

V # #

7 4 0 6

1 4 0 1 2

A

B

D

C

E

F

G

1 , 4 0 0 1

4 5 1 1

&$C#

L T

$ IL !

a'(de) *

V # #7 4 0 8

+

I

4 0 1 9 2

J

1

J

2

J

3

J

4

!

C

"

C

#

R

S

T

Q

1

Q

2

Q

3

Q

4

$

%

C

&

7 4 1 1

1 0 1 0 6

7 4 0 8

4 0 1 9 2

J

1

J

2

J

3

J

4

!

C

"

C

#

R

S

T

Q

1

Q

2

Q

3

Q

4

$

%

C

&

1 , 4 0 0 1

7 4 0 6

1 4 0 2 5